Vectored interrupt support 3. Can handle multiple interrupts.

Systick Timer Interrupt Programming Tm4c123 Arm Cortex M4 Arm Cortex Timer Interrupting

So heres a tutorial on how to use it The NVIC on the STM32F4 uses 4 bits to define priority levels.

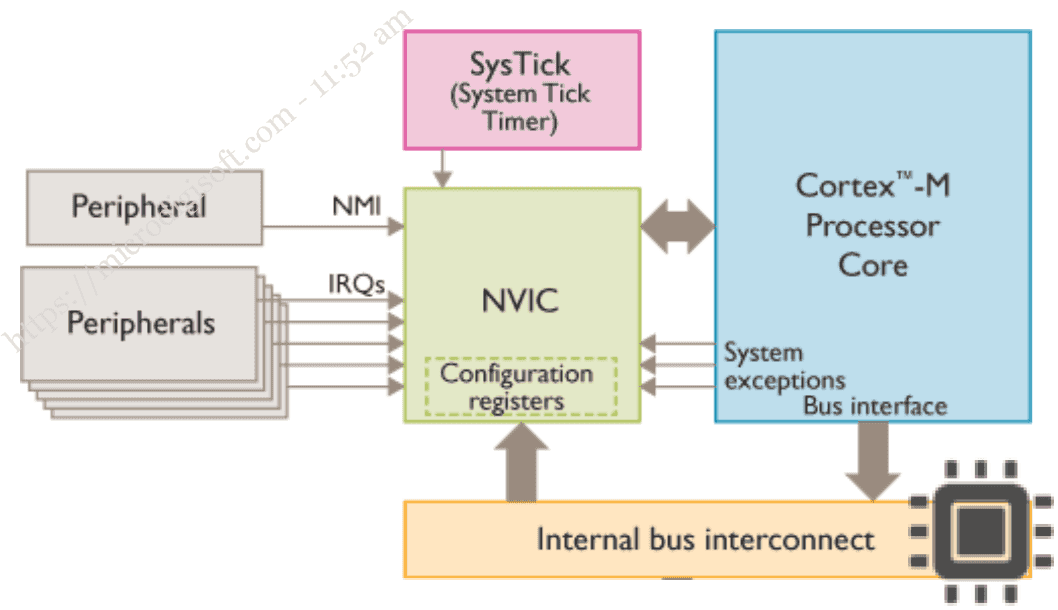

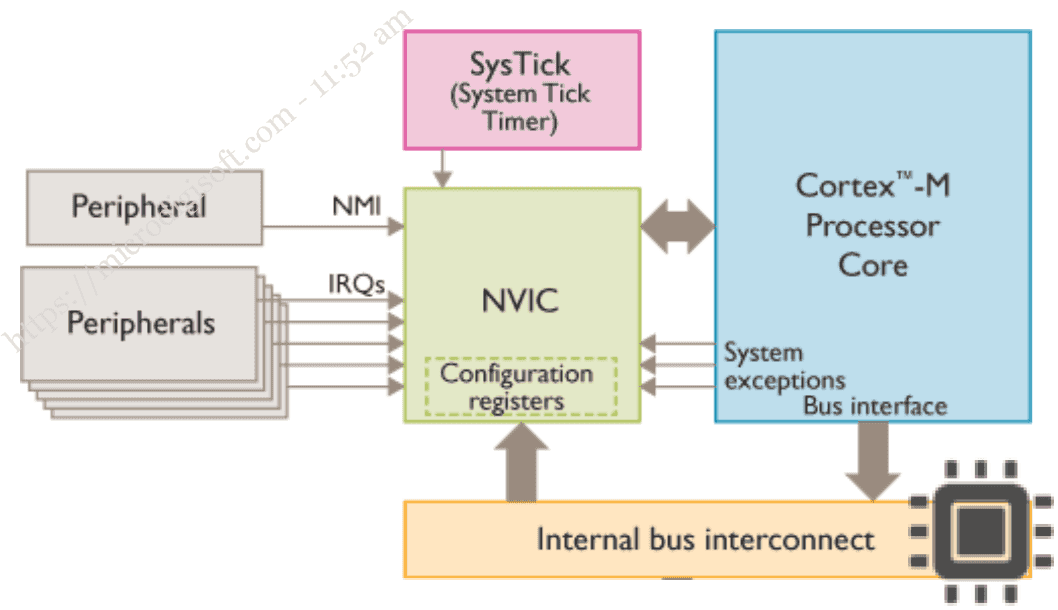

. Accessing the Cortex-M3 NVIC registers using CMSIS. The main features are. It supports the system exception and interrupt occurrence.

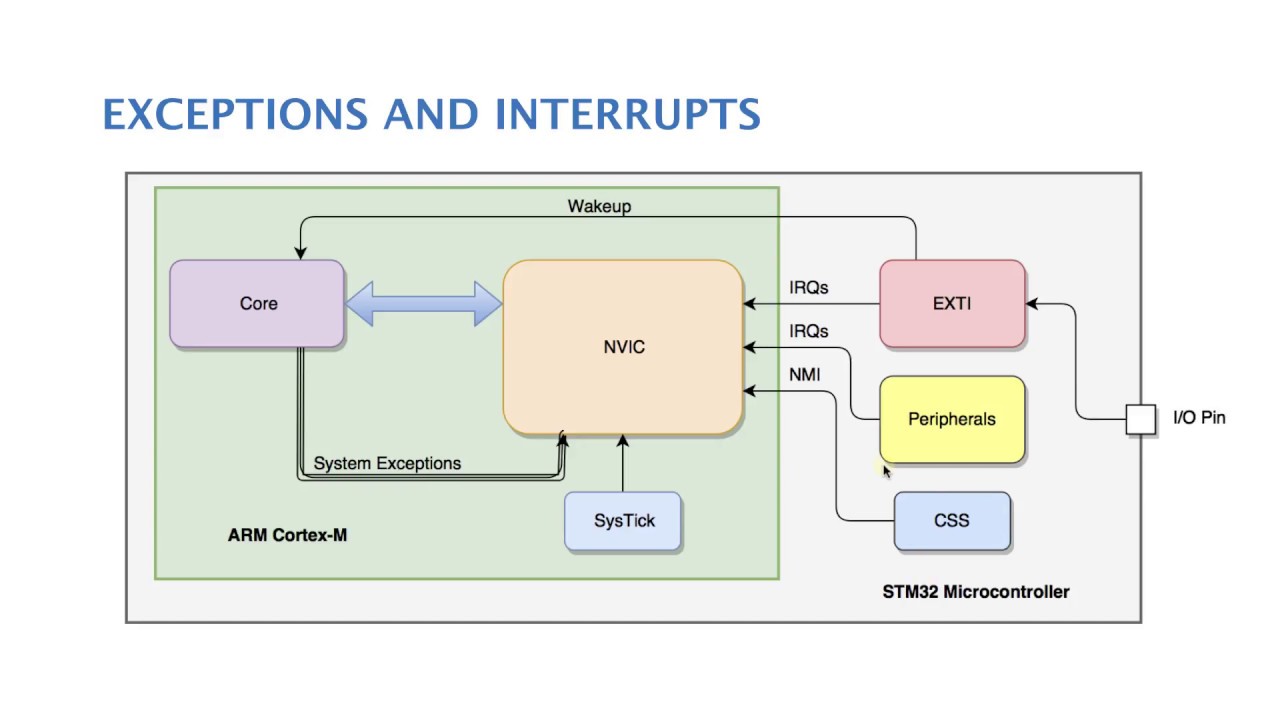

Please Mind The Interrupt Event Posted in ARM Featured Microcontrollers Slider Software Development Tagged EXTI interrupts Nested Vector. It is closely linked to the CPU core logic and Its control registers are accessible as memory mapped. The priority for each interrupt source is programmable four levels.

Modified 5 years 10 months ago. Nested Vectored Interrupt Controller. ESP8266 ESP32 Projects.

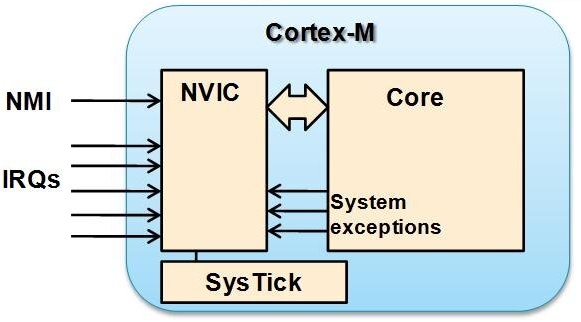

Nested Vector Interrupt Controllers or NVIC for short have two properties. NVIC usage hints and tips. This module provides the processors outstanding interrupt handling abilities.

Level-sensitive and pulse interrupts. What is nested vector interrupt control. Nested Interrupt Processing Nested Vector Interrupt Controller.

Nested Vector Interrupt Controller. Leave a Comment Cancel reply. It provides the following features.

Nested Vector Interrupt Controllers or NVIC for short have two properties. Nested Vectored Interrupt Controller. Nested interrupt support 2.

Find out more information. Seek to live currently behind live LIVE. If two pending interrupts share the same priority priority is given.

A programmable priority level for each interrupt. Interrupt Active Bit Registers. SCI SMI NMI and normal Interrupt.

Continue reading Bare-Metal STM32. So it has 16 programmable priority levels. The NVIC block suspends the calculation processing that is running on the main core and controls switching to prioritized processing.

Nested vector interrupt controller. So it has 16 programmable priority levels. So heres a tutorial on how to use it The NVIC on the STM32F4 uses 4 bits to define priority levels.

Electronics Components Tutorials. Facebook Twitter LinkedIn Printer Video Player is loading. The number of interrupts implemented is device-dependent.

Level-sensitive and pulse interrupts. This section describes the NVIC and the registers it uses. Cortex-M0 Nested Vector Interrupt Controller.

Leave a Reply Cancel reply. Nested Vectored Interrupt Controller Nvic Arm Cortex M Understanding the STM32 NVIC Nested Vectored Interrupt. If a high-priority exception interrupt is required during exception processing then the NVIC block.

Understanding the STM32 NVIC Nested Vectored Interrupt Controller The NVIC on the STM32 series of ARM Cortex-M micro-controllers is a very powerful tool that can be used to handle any type of interrupt. 32 interrupt sources 4 programmable priority levels low-latency exception and interrupt handling Automatic nesting Power management control Applications can benefit from dynamic prioritization of the interrupt levels fast response to the. We are enabling line 13 interrupt management on the NVIC Nested Vectored Interrupt Controller which is a special component in charge for the interrupt handling.

Nested Vectored Interrupt Controller The Nested Vectored Interrupt Controller NVIC is an integrated part of the Cortex M3M4 processor. Remaining Time - 1x. Interrupt Clear-enable Registers.

Viewed 3k times. Nested Vectored Interrupt Controller. It supports up to 256 different interrupt vectors.

Your email address will not be. If a high-priority exception interrupt is required during exception processing then the NVIC block. Defferent peripheral can trigger interrupt like data come to USART ADC finished conversion timer overflow and more more.

Software Trigger Interrupt Register. Nested Vector Interrupt Controller. NVIC usage hints and tips.

It supports the system exception and interrupt occurrence. Nested Vectored Interrupt Controller. Home Tutorials Microcontrollers STM32 Vectored Interrupt Controller and Nested Vectored Interrupt Controller VIC and NVIC Nested IRQ.

Current Time Duration. Breakpoint inside interrupt C. The ARM Cortex -M0 Nested Vector Interrupt Controller NVIC provides an interface between interrupt sources external to the core peripherals and external pins and the core.

Ask Question Asked 5 years 10 months ago. System control block. NVIC or Nested Vector Interrupt Controller is used to dinamically tell which interrupt is more important and for enabling or disabling interrupts.

Notify me of new posts by email. Interrupt vector and irq mapping in do_IRQ. Differences among various interrupts.

The interrupt controller belongs to the Cortex-M0 CPU enabling a close coupling with the processor core. NVIC Nested Vectored Interrupt Controller The NVIC block suspends the calculation processing that is running on the main core and controls switching to prioritized processing.

Vectored Interrupt Controller Vic And Nvic

Nested Vectored Interrupt Controller Nvic Arm Cortex M

Vectored Interrupt Controller Vic And Nvic

Vectored Interrupt Controller Vic And Nvic

What Is Nested Vector Interrupt Control Nvic

Stm32wl 5 System Nested Vectored Interrupt Control Nvic Youtube

الدرس ٩ Arm Cortex M4 Nested Vectored Interrupt Controller Nvic Youtube

0 comments

Post a Comment